アーカイブ情報

2026/5/8

【AWARD】レゾナックと電力中央研究所の「パワー半導体用高品質SiCエピウェハーの高生産性製造技術」、「市村産業賞」貢献賞受賞

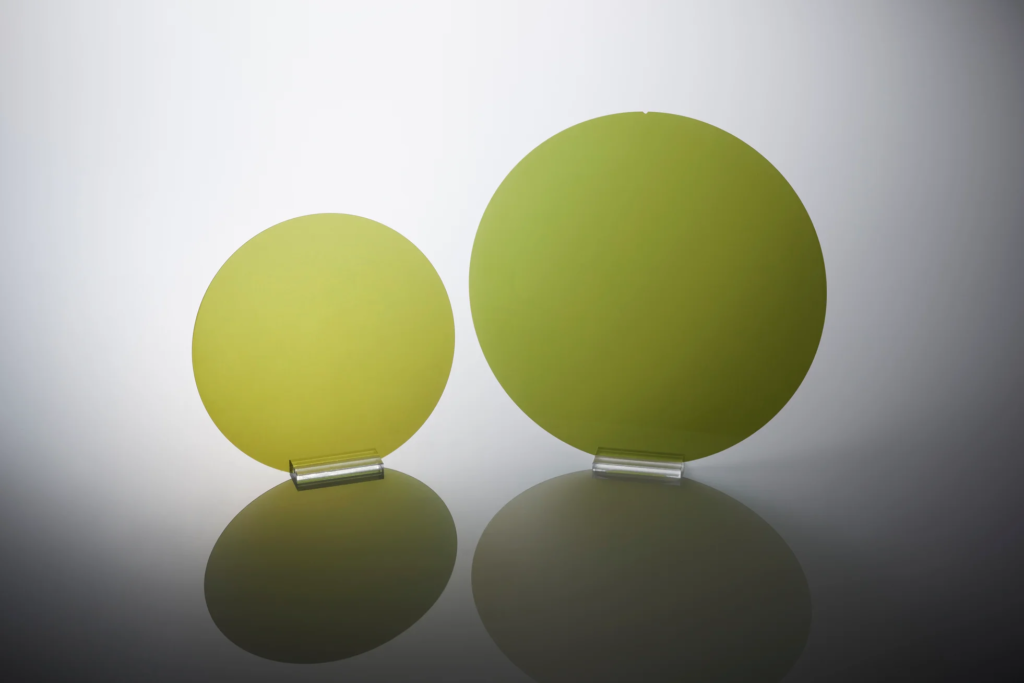

レゾナックと電力中央研究所は、「パワー半導体用高品質SiCエピタキシャルウェハー(エピウェハー)の高生産性製造技術」の開発において、市村清新技術財団が主催する第58回市村産業賞「貢献賞」を共同で受賞した。この技術は、次世代パワー半導体材料として注目されるSiC(シリコンカーバイド)エピウェハーの高品質化と高生産性の両立を実現するものであり、レゾナックは電力中央研究所との共同研究を基盤に、装置メーカーとの技術連携やデバイスメーカーなどからの評価・フィードバックを取り入れるなど、さまざまなパートナーとの共創の積み重ねにより開発を進めてきた。EV(電気自動車)、データセンター電源、鉄道、電力制御機器などにおける省エネルギー化と高効率化への貢献が期待されている。

受賞技術の概要

地球温暖化対策としてCO2排出量削減が求められる一方、エネルギーの電化やAI拡大などにより、世界的に電力需要の増加が見込まれている。こうした中、電力変換効率を高めるパワー半導体の重要性が高まっており、従来のシリコン(Si)の物性限界を超える特性を持つSiCパワー半導体が注目されている。しかし、その普及拡大には、SiCエピウェハー(SiC基板上にSiCエピ膜を成膜したウェハー)の高品質化と低コスト化が課題となっていた。

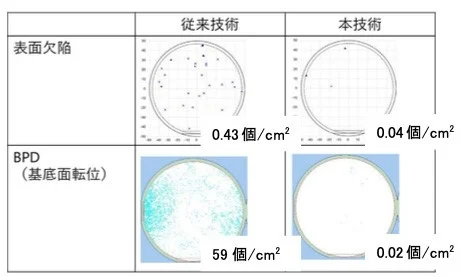

レゾナックと電力中央研究所は、この課題に対し、SiCエピ膜の高品質化と高生産性を両立する製造技術を開発。従来、成膜中に装置内部で生成される副生成物(デポ)がパーティクル(異物)として基板上に落下する現象により、エピ膜の表面欠陥が発生していたが、この技術では、高品質化にむけた技術開発により以下の4点を実現している。

1.本現象を根本的に抑制する装置設計により、表面欠陥を低減

2.基板から伝播する内在欠陥である基底面転位(BPD)を大幅に低減する界面制御プロセス技術を確立

3.表面欠陥、基底面転位の欠陥を高精度に検出する量産検査技術を活用し、大量生産における欠陥発生要因を定量的に把握することにより量産レベルでの安定した低欠陥化を達成

4.高温搬送や低熱容量化により昇降温時間を短縮し、生産性を向上

技術の効果と今後の展望

この技術により、SiCパワーデバイスの初期電気特性の歩留まりおよび長期信頼性が向上し、デバイスの低コスト化と車載や鉄道用途で求められる高い信頼性の確保に貢献している。これによりパワーデバイス分野でのSiCの採用が進み、EVでは航続距離の向上(電費改善)、データセンターの電源設備や鉄道、再生可能エネルギーの系統連系では大幅な省エネルギー化といった効果をもたらしている。

今後は、これらの分野に加え、より大容量の電力を扱う電力制御機器などへの適用拡大を通じて、電力インフラの高度化やエネルギー利用効率の向上への貢献が期待される。

- カテゴリー

- コンバーティングニュース