アーカイブ情報

2026/4/9

【Coating】クオルテック、ユニバーサルめっきによる新規コーティング技術「MAP(Mist-Assisted universal Plating)プロジェクト」の開発テーマ発表

クオルテックは、立命館大学総合科学技術研究機構の高橋 勲教授と共同で進めている、ユニバーサルめっきによる新規コーティング技術「MAP(Mist-Assisted universal Plating)プロジェクト」の開発テーマの詳細について発表した。

■MAPプロジェクトとは

このプロジェクトでは、貴金属価格の高騰や国際的な環境規制への対応といった課題を背景に、安定供給可能な低コストかつ環境配慮型技術として、ユニバーサルめっきによる新たなコーティング技術の確立を目指す研究開発を進めている。同社は、2025年9月に立命館大学びわこ・くさつキャンパス テクノコンプレクス産学連携ラボラトリーに研究開発拠点を開所した。この度、研究開発の環境構築を終え、上述の課題に対応するための開発テーマを設定した。

■開発テーマ

「低環境負荷のユニバーサルめっきを用いた次世代半導体用ガラスコア基板の実用化開発」

従来のめっき技術では、絶縁体であるガラスに直接銅めっきを施すことは困難であったが、同社では、ミストCVDを応用した新しい成膜技術「ユニバーサルめっき」を用いて、ガラス上に低抵抗な金属銅の成膜を行う技術を開発した。この技術を用いると、次世代の半導体パッケージに利用されるガラスコア基板やインターポーザ基板への応用が可能であり、半導体の高性能化に繋がる。さらにめっきからの技術移管が進めば、めっき工程で大量に使用される有害な薬液を100分の1以下に減らし、環境負荷を大幅に低減することが可能となる。

・ユニバーサルめっきの特徴

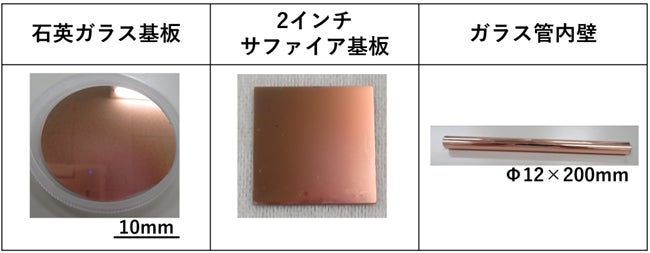

ユニバーサルめっきは銅が溶けた液体を蒸発させることで基材表面に金属の銅が付着するため、基材の種類に限らず銅膜のコーティングを行うことができる。図1に実際に成膜した部材の写真を示す。鏡面研磨して平坦性の高い石英ガラスや半導体用のサファイア基板の表面にも成膜できている。これらの試料についてめっきの密着試験(JIS H 8504準拠)を実施すると、検査をクリアできるほど銅膜と基材が密着した膜が形成される。さらに従来法では非常に困難であったガラス管内壁に均一に成膜できることも優位性のある特徴。この特徴を用いると、導電性を付与した長尺のガラスの管を作製することができる。

・次世代半導体パッケージ基板への活用

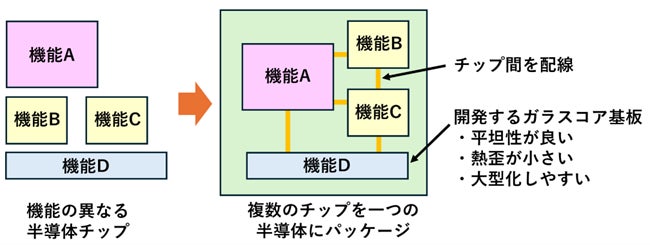

近年、生成AIの急速な普及等により半導体のさらなる高性能化、低コスト化が求められている。半導体の高性能化のためには、半導体チップ内の回路を細線化するいわゆる前工程に関わる技術開発があるが、技術的な限界に近付いております。また、小型化、軽量化のために一つのチップの中に演算、記録、センサー等の様々な機能を持たせたSoC(System on a chip)技術が発展した。

しかし、この方法ではチップの一部分に不良が発生した場合、チップ全体が使用できず歩留まりが低下することや、一部分の仕様変更を行う場合すべてを作り変える必要があり、コストがかかる。そこで、図2のように、複数のチップを一つの半導体パッケージに集積するチップレット技術が低コストと高性能化を両立する解決策として注目されている。この方法では、大きな半導体チップの中に複数の小さなチップを作製し切り分けるため、不良発生時のロスを大きく低減できる。また、仕様変更や機能拡張を行う場合も個別のチップの組合せを変えるだけで対応できる。さらに異なるメーカーのチップを組み合わせるなど柔軟な製品開発が可能になる。このチップレット技術はミクロン単位の配線が必要となるため、従来の樹脂製の基板では平坦性が悪く実現が困難であった。そこで、平坦性が高く、チップ発熱時のひずみが小さいガラス基板が注目を集めている。同プロジェクトでは、このチップレット技術に適用されるガラスコア基板の開発を進めていく。

・ガラスコア基板実用化のための課題

ガラスコア基板への実用化のためには、ユニバーサルめっきで作製した銅膜とガラスの密着強度の向上と大型化が必要となってくる。現状では、めっきの密着試験(JIS H 8504準拠)の一部はクリアしている状態だが、製品化のためにはユニバーサルめっきの成膜条件を最適化し密着性を上げる必要がある。また、現在は4インチ径の材料への成膜は可能ですが、300mm角以上の大面積のガラス基板へ均一に成膜しなければない。これについては、成膜装置の構造などを検討し実現を目指す考えだ。

■研究開発成果及び期待される効果

今回の開発で作製されるガラスコア基板を活用しチップレット技術が普及すれば、AIや自動運転等に必要な高性能の半導体を歩留まり良く安価に製造できるようになる。さらに、製品開発の柔軟性が上がることで特定の用途に最適化された製品を短い開発期間で市場投入できる等大きなメリットがある。

■第73回応用物理学会春季学術講演会での発表

立命館大学総合科学技術研究機構の高橋 勲教授が、3月15日に東京科学大学大岡山キャンパスにて開催された第73回応用物理学会春季学術講演会のポスターセッションで当研究に関する発表を行った。

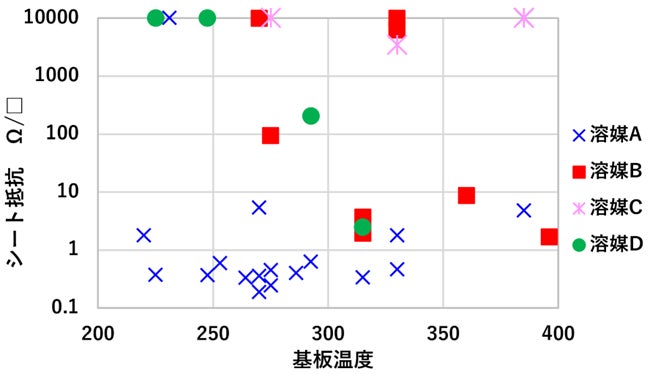

この発表では、銅原料や溶媒の種類、基板温度などユニバーサルめっきの成膜条件と密着性や抵抗値との関係を報告した。一例として、図3に様々な溶媒を用いた時の基板温度とガラス上の銅膜のシート抵抗の値との関係を示す。シート抵抗の値は溶媒の種類に大きく依存しますが、特定の溶媒で広い温度帯域において1Ω/□以下の低いシート抵抗が得られた。最も良い値はシート抵抗約0.3Ω/□、比抵抗約5mΩcmとなった。この値は金属銅の値と比べ遜色ないレベルにある。

■今後の流れ

各テーマにおいて、現時点で有望な兆しが確認でており、引き続き、立命館大学総合科学技術研究機構の高橋 勲教授と共同で研究開発を進めていく。今後進展があり次第、随時発表する。

■まとめ

MAPプロジェクトは、従来の成膜技術が抱える「コスト」「環境負荷」「適用制約」という課題を解決する可能性を持つ革新的技術である。同社は今後も、「未来品質」を支えるコーティング技術の確立と社会実装を通じて、次世代産業の発展に貢献していく。

- カテゴリー

- コンバーティングニュース