アーカイブ情報

2025/12/9

【ナノインプリント用テンプレート】大日本印刷、最先端半導体向けの回路線幅10nmの型を開発

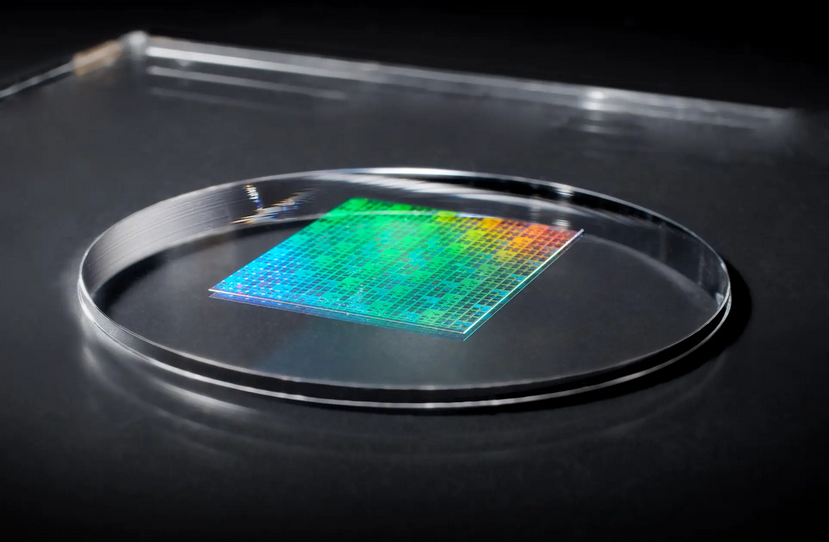

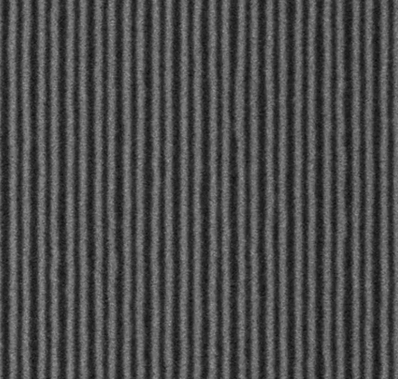

大日本印刷(DNP)は、半導体の回路パターンの形成に使用するナノインプリントリソグラフィ(Nano-Imprint Lithography:NIL)*1向けに、1.4ナノメートル(1nm=10億分の1メートル)世代相当のロジック半導体にも対応可能な、回路線幅10nmのテンプレート(型)を開発した。今回開発した線幅10nmのNIL用テンプレートは、NAND型フラッシュメモリーに加え、スマートフォンやデータセンターなどで使用される最先端ロジック半導体の微細化ニーズに応える。

NIL用テンプレート開発の狙いと経緯

近年、多様な機器の高性能化にともない、先端半導体では一層の微細化が求められており、EUV(Extreme Ultra-Violet:極端紫外線)リソグラフィによる生産が進んでいる。一方で、生産ラインの構築や露光工程に比較的多くのコストや電力が必要となるため、製造コスト削減と環境負荷低減の両立が急務となっていた。DNPは2003年から、回路パターンを刻んだテンプレートを基板に直接圧着して転写することで、露光工程の電力消費量を抑制できるNIL用テンプレートの開発し、独自のノウハウを蓄積してきた。

今回、EUVリソグラフィの一部工程の置き換えや、EUVリソグラフィの生産プロセスを持たない顧客のニーズに対応し、先端領域のロジック半導体の製造を可能にする回路線幅10nmのNIL用テンプレートを開発した。DNPは、このテンプレートの供給を通じて、顧客の半導体製造プロセスの選択肢を拡大し、製造コスト削減と環境負荷低減の両立につなげていく。

新たに開発した回路線幅10nmのNILテンプレートの特長

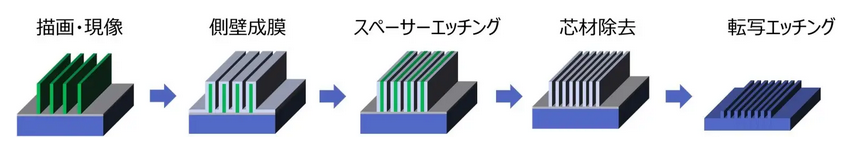

○描画装置によって形成したパターンに成膜・エッチングを施してパターンの密度を2倍にするダブルパターニング(Self-Aligned Double Patterning:SADP)を活用して、NILテンプレートの微細化を実現した。

○DNPが培ってきたフォトマスク製造の技術・ノウハウに加え、ウエハの製造プロセスの技術も応用し、回路線幅10nmのNILテンプレートを開発した。

○今後さらなる拡大が見込まれる先端ロジック半導体の回路線幅の微細化ニーズに対応する。

○先端半導体製造の露光工程での電力消費量を削減します。「NILによる超微細半導体の省エネルギー加工技術」により、従来のArF(フッ化アルゴン)液浸やEUVなどの露光工程と比較して、電力消費量を約10分の1に抑えることができる。*2

今後の展開

DNPは半導体メーカー等の顧客との対話を深め、半導体の微細化ニーズなどを先取りし、NIL用テンプレートの評価ワークを開始しており、2027年に量産開始を目指す。引き続き、半導体のさらなる微細化やコスト削減に向けて、NIL用テンプレートの一層の開発や需要拡大に対応した生産体制の強化を進め、2030年度にNILで40億円の売上増加を目指す。

なお、同製品は、2025年12月17日~19日に東京ビッグサイト(国際展示場)で開催される「SEMICON Japan 2025」のDNPブース(東6ホール・小間番号:E5936)で展示される。

*1 ナノインプリントリソグラフィ:基材上の樹脂などに金型のテンプレートを圧着し、nm(ナノメートル:10-9メートル)~μm(マイクロメートル:10-6メートル)単位の線幅の回路パターンを安定的かつ安価に転写する微細加工技術。

*2 NILによる超微細半導体の省エネルギー加工技術 → https://www.dnp.co.jp/news/detail/10162455_1587.html

- カテゴリー

- コンバーティングニュース