アーカイブ情報

2025/8/20

【ポスト5G/6G】キオクシア、NEDOの委託事業で大容量(5TB)・広帯域(64GB/s)のフラッシュメモリモジュールの試作に成功

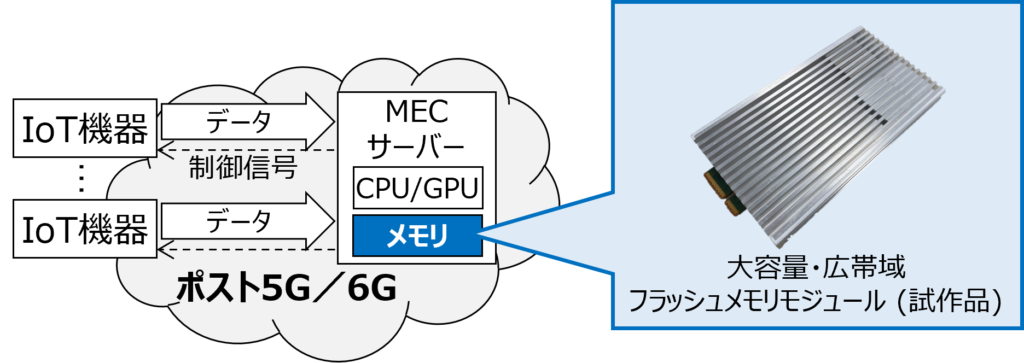

ポスト5G/6Gでは、無線ネットワークの高速化・低遅延化・多数同時接続がさらに進む一方で、データを遠方のクラウドサーバーに送信して処理すると、有線を含むネットワーク全体の遅延が大きくなり、リアルタイムでの応用が困難になる。このため、ユーザーに近いエリアでデータを処理するMECサーバーの普及が求められており、MECサーバーの活用による各種産業のDXが期待されている。さらに、近年は生成AIなどの高度なAI活用のニーズが高まっており、MECサーバーの性能向上と併せて、メモリモジュールにも一層の大容量化と広帯域化が求められている。

このような背景を踏まえ、NEDO(新エネルギー・産業技術総合開発機構)が実施する「ポスト5G情報通信システム基盤強化研究開発事業」※1において、キオクシアはフラッシュメモリを用いてメモリモジュールの大容量化と広帯域化に取り組み、容量5TB・帯域64GB/sのメモリモジュールの試作に成功し、動作の実証を行った。

今回の成果は次の通り。

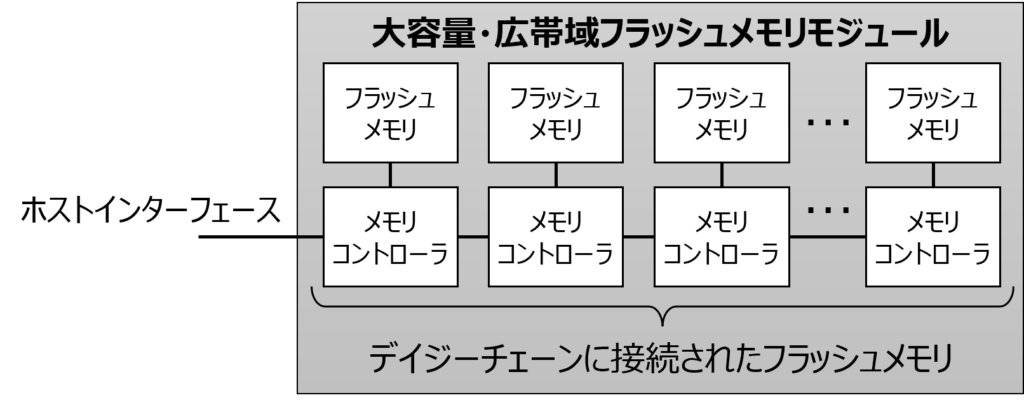

(1)デイジーチェーン接続の採用

メモリモジュールの大容量化と広帯域化を両立するために、複数のフラッシュメモリをバス接続する代わりに、コントローラを介して数珠つなぎするデイジーチェーン接続(図2)を採用。これにより、フラッシュメモリの数を増やしても帯域が劣化せず、従来の限界を超えた大容量化を実現した。

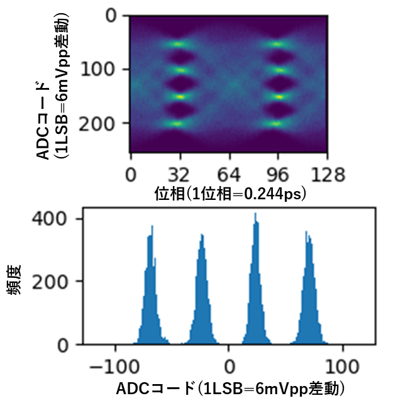

(2)128GbpsでのPAM4※2高速・低電力通信技術の開発

メモリコントローラ間のデイジーチェーン接続には、配線数を抑制するために、パラレル接続ではなく、差動信号を用いた高速シリアル通信を適用し、さらに広帯域化するために、多値変調方式PAM4を採用することで、メモリコントローラ間の128Gbpsでの高速通信を低電力で実現した(図3)。

(3)フラッシュメモリ性能改善技術の開発

メモリモジュールに搭載するフラッシュメモリの読み出し遅延を改善するため、連続アクセス時にデータを事前に読み出すことで遅延時間を最小限に抑えるフラッシュプリフェッチ技術を開発し、コントローラに実装した。また、メモリコントローラとフラッシュメモリ間のインターフェースに信号低振幅化とゆがみ補正・抑制技術を適用することで、帯域を4.0Gbpsに高速化した。

(4)メモリコントローラおよびメモリモジュールの試作

128GbpsでのPAM4高速・低電力通信技術とフラッシュメモリ性能改善技術を適用し、サーバーとのホストインターフェースにPCIe®6.0※3(64Gbps、8レーン)を採用したメモリコントローラおよびメモリモジュールを試作し、容量5TB・帯域64GB/sのメモリモジュールを40ワット(W)以下で実現できることを実証した。

今後、キオクシアは、今回の研究成果の社会実装に向けて、エッジでのIoT・ビッグデータ解析や高度なAI処理に加え、生成AIなど新たな市場トレンドを捉えて、早期の実用化・事業化を推進する。

NEDOは、今後もポスト5Gに対応した情報通信システムの中核となる技術を開発することで、日本のポスト5G情報通信システムの開発および製造基盤の強化を目指す。

※1 ポスト5G情報通信システム基盤強化研究開発事業

事業名:ポスト5G情報通信システム基盤強化研究開発事業/ポスト5G情報通信システムの開発/広帯域大容量フラッシュメモリモジュールの研究開発(委託)

事業期間:2021年度~2024年度

事業概要:ポスト5G情報通信システム基盤強化研究開発事業

※2 PAM4

4-level Pulse Amplitude Modulationの略。電気信号の電圧レベルを0と1の2値(1ビット)とする従来の通信方式に対して、電圧レベルを4値(2ビット)とする通信方式。従来比2倍の通信容量が実現できるため、50Gbpsを超えるシリアル通信に採用されている。

※3 PCIe®6.0

PCIeは、PCI-SIGの登録商標。

- カテゴリー

- コンバーティングニュース