アーカイブ情報

2026/4/9

【ロジックチップ用成膜装置】アプライド マテリアルズ、オングストローム時代のロジックチップ用成膜装置を発表

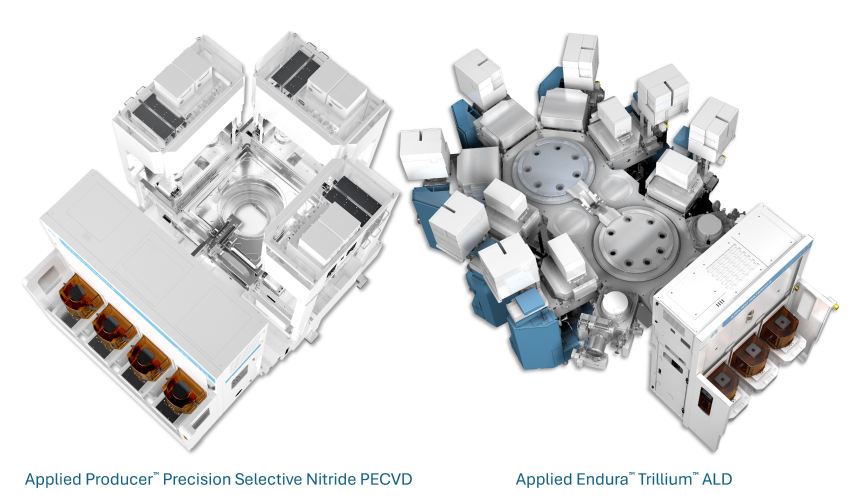

•3D Gate-All-Aroundトランジスタに向けた原子スケールの微細構造を形成する半導体製造装置

•Precision™ Selective Nitride PECVDはシャロー トレンチ アイソレーションの完全性を保ちながら寄生容量を低減、チップの電力効率を大幅に改善

•Trillium™ ALDはシリコン ナノシートを複雑なメタルゲートスタックで囲み、広範なAIコンピューティング用途に最適化されたトランジスタを実現

•複数の大手ファウンドリ/ロジックメーカーが2nm以降のプロセスに新装置を活用

アプライド マテリアルズ(Applied Materials, Inc., Nasdaq AMAT、本社:米国カリフォルニア州サンタクララ)は4月8日(現地時間)、世界最先端ロジックチップの極めて微細な構造を形成する半導体製造装置2機種を発表した。材料成膜を原子レベルの精度で制御し、より高速かつ電力効率の高いトランジスタの量産化を通じてグローバルなAIインフラの拡大ペースを維持する。

AIコンピューティング需要の急増を背景に、半導体業界はプロセッサチップ内に数千億個搭載されるトランジスタ1個当たりから、より高いエネルギー効率性能を引き出すため、スケーリングの限界に挑戦している。この課題に応えるべく、世界有数のロジックメーカー各社は2nmノード以降で新たなGate-All-Around(GAA)トランジスタを導入している。GAAへの移行により、同一消費電力での性能が大幅に向上する一方で、これを実現するプロセスの複雑性は劇的に増大する。GAAトランジスタ内部の複雑な3D構造を形成するためには500を超える工程が必要となり、その多くで、原子サイズに迫る厳しい公差内で、これまでにない精度・再現性・制御性を持つ成膜技術が求められる。

同社が発表した2つの半導体製造装置は、マテリアルイ ノベーションを活用し、GAAトランジスタに用いるきわめて複雑な微細形状を形成するもの。これらの新技術は、先進チップの性能と電力効率を大きく左右する重要な金属や絶縁材料の成膜を可能にする。

アプライド マテリアルズのセミコンダクタ プロダクトグループ プレジデント、プラブー・ラジャは次のように述べている。「業界は非線形に急変する時代を迎えつつあり、もはや従来のリソグラフィによるチップスケーリングだけでは不十分です。最先端のロジックノードはオングストローム レベルに達しており、チップの性能と電力効率はマテリアルに大きく依存します。アプライド マテリアルズはマテリアル エンジニアリング分野における創業以来のリードを生かし、画期的なトランジスタを生むこれらの製造装置をお客様に提供して、AIコンピューティング ロードマップの基盤を固めます。」

Precision™ Selective Nitride PECVD:シャロー トレンチ アイソレーションの完全性を維持

開発が進む次世代AI用のGPUでは、切手1枚ほどの面積に3,000億個以上ものトランジスタが集積されると見込まれている。その際に絶縁分離(アイソレーション)が不十分だと、隣り合うトランジスタ間で電子が拡散し、寄生容量が発生するほか、不測の電気的相互作用が生じて、信号の遅延、電力のロス、チップの電力効率(performance-per-watt)低下などを引き起こす恐れがある。

先進的トランジスタ アーキテクチャでは、隣接するトランジスタを電気的に分離する手法としてシャロー トレンチ アイソレーション(STI)が用いられる。具体的には、トランジスタ間の表面にトレンチ(溝)をエッチングし、そこに酸化シリコンなどの絶縁材料を埋め込んで、電荷を隔離し不要なリークを防止する技法。しかし、GAAデバイスにおけるSTIは極めて微細であるため、量産工程を通じて絶縁性能の維持が困難です。溝が形成された後、多数の後続工程を経るため、その過程で絶縁材料である酸化シリコンが徐々に損耗し、チップ全体の性能に悪影響を及ぼす恐れがある。

Applied Producer™ Precision™ Selective Nitride PECVD*では、業界初の選択的ボトムアップ成膜プロセスにより、トレンチ内で必要な部分にのみ窒化シリコンを成膜することができる。さらに、酸化シリコンの上に高密度の窒化シリコンを成膜することで、後工程によるリセスを防ぎ絶縁性が維持される。低温プロセスのため、下層の薄膜や構造体への損傷も回避できる。絶縁溝の形と高さが元のままなので、電気的特性が一定に保たれ、寄生容量やリーク電流が減少し、デバイス全体のパフォーマンスが大幅に向上する。

現在、複数の大手ロジックチップメーカーが2nm以降のGAAプロセスノードにPrecision Selective Nitride PECVDの採用を進めている。

Trillium™ ALD:原子スケール均一性で複雑な金属ゲート構造を形成

個々のGAAトランジスタはスイッチとして機能する。複数のメタル層からなるゲートスタックはしきい値電圧を決定し、トランジスタのオン・オフを制御する。データセンターからエッジに至るユニークな各種AIワークロードに対応するため、ピークパフォーマンス用にチューニングされた高速スイッチや、電力使用を最小化するようチューニングされたスイッチなど、広範なトランジスタ設計オプションがチップメーカーから提供されている。こうしたトレードオフの鍵となるのが、高精度メタル成膜を活用したメタルゲートスタックの最適化。

GAAトランジスタでは、10nm(ヒトの毛髪の約1万分の1)間隔で平行に配置された複数のナノシートの周囲を、ゲートスタックがくまなく覆う。ゲートスタックにギャップや不均一があると、トランジスタのスイッチング特性にばらつきが生じ、チップの性能、消費電力、信頼性、歩留まりに悪影響が及びかねない。従来のメタル成膜手法では、こうした究極の要求に応えるのは困難であった。

Applied Endura™ Trillium™ ALD**は、きわめて複雑なGAAトランジスタ ゲート スタックに精密なメタル成膜を施すよう設計されたIntegrated Materials Solution™。この装置は、アプライド マテリアルズがメタルALD技術で培ってきたリーダーシップを先進トランジスタ アプリケーションに応用したもの。複数のメタル成膜ステップを単一プラットフォームにインテグレートしたTrilliumは、各種のトランジスタに合わせた柔軟なしきい値電圧のチューニングを可能にしている。半導体業界史上最も大きな成功を収めたEnduraプラットフォームの超高真空技術により、クリーンルーム内の不純物からウェーハを保護し、ナノシート間の極微小空間でも高品質な成膜を実現する。メタルゲートスタック層の厚さをオングストロームレベルで制御することで、Trillium ALDは先進GAAトランジスタに求められるチューニング性と信頼性を確保し、トランジスタの性能、電力効率、信頼性を高める。

アプライド マテリアルズのTrillium ALDは、複数世代のFinFETプロセスノードでメタルゲートスタック成膜のベンチマークとして定評を得ている。GAA構造の限定されたスペースに対応するため、より薄い仕事関数金属や界面ダイポール材料を扱える新機能を追加するなど、GAAアプリケーションへの特化を進めてきた。現在は複数の大手ロジックチップメーカーがTrillium ALDを2nm以降のGAAプロセスノードに採用しつつある。

* PECVD = プラズマCVD(プラズマ強化化学気相成長)

**ALD = 原子層堆積

- カテゴリー

- コンバーティングプロダクツ&テクノロジー