アーカイブ情報

2026/1/13

【半導体】キヤノン、ナノインプリントリソグラフィ技術を応用した「Inkjet-based Adaptive Planarization」技術を世界で初めて実用化

キヤノンは、ナノインプリントリソグラフィ(NIL)技術を応用し、ウエハーを平坦化する「Inkjet-based Adaptive Planarization」(IAP)技術を開発し、世界で初めて※1 実用化した。ロジックやメモリーなどの先端半導体製造現場での活用に向けて、2027 年中にIAP 技術を用いた装置の製品化を目指す。

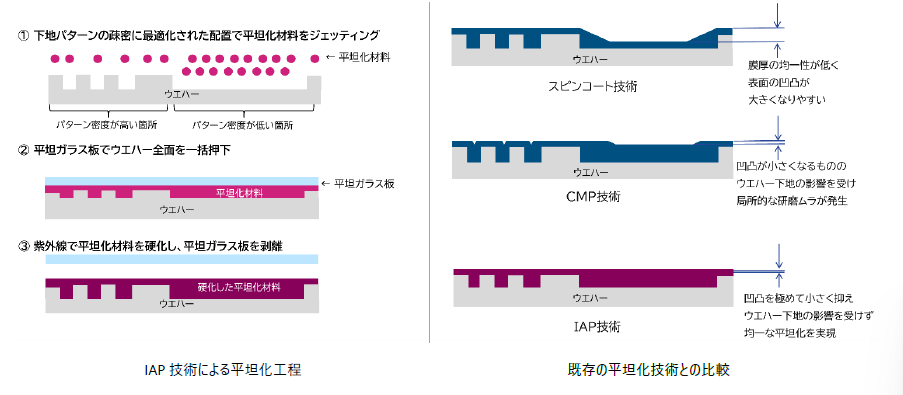

半導体製造では、成膜や配線などの工程を重ねる中で生じるウエハー表面の凹凸を均一に整える、平坦化工程が不可欠である。特に、微細化や3D 化が進む先端半導体では、ウエハー表面のわずかな凹凸が、CD※2 誤差やパターンエッジの位置ずれにつながり、歩留まりや生産性に大きな影響を与えることから、これまで以上に高精度な平坦化技術が求められている。現在主流の平坦化手法は、薄膜を形成し表面をなだらかにするスピンコート技術や、研磨を繰り返すCMP(Chemical Mechanical Polishing)技術ですが、工程の複雑化やコスト増加が課題となっている。

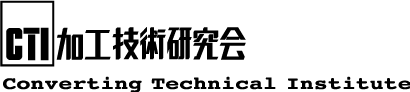

キヤノンは、インクジェット方式でレジスト(樹脂)を塗布したウエハーに、回路パターンを刻み込んだマスク(型)をハンコのように押し当てて回路を転写するNIL 技術を開発し、半導体製造装置「FPA-1200NZ2C」を2023 年10 月に発売した。今回開発したIAP 技術は、このNIL 技術を平坦化用途に応用したもの。ウエハー表面の凹凸

分布に応じて、インクジェット方式で平坦化材料(樹脂)を最適に配置し、その上から平坦ガラス板を押し当てる。

これにより、凹凸の粗密や回路パターンの違いに左右されることなく、直径300mm のウエハー全面を一括の押印工程で高精度に平坦化することが可能です。ウエハー表面の凹凸を5nm 以下に抑えることができ、後続の工程に不可欠な、より均一な層構造を実現する。

キヤノンは、今後も、半導体製造技術や装置に関する研究開発を進め、半導体の進化と製造現場の生産性向上に貢献していく。

※1 2026 年1 月12 日現在(キヤノン調べ)。

※2 Critical Dimension。半導体デバイス性能に影響する回路の最小寸法のこと。

- カテゴリー

- コンバーティングニュース