アーカイブ情報

2025/10/10

【半導体製造装置】アプライド マテリアルズ、AIのパフォーマンスを飛躍的に向上させる「Kinex」「Xtera」「PROVision 10」発表

アプライド マテリアルズ(Applied Materials, Inc.、本社:米国カリフォルニア州サンタクララ、社長兼 CEO ゲイリー・E・ディッカーソン)は2025年10月7日(現地時間)、AIコンピューティングの基盤となる先進的ロジックやメモリチップの性能を高める新しい半導体製造装置を発表した。これらの新製品は、より強力なAIチップを実現するための3つの重要分野、すなわち最先端ロジック(Gate-All-Around [GAA]トランジスタを含む)、高性能DRAM(高帯域幅メモリ[HBM]を含む)、およびチップ性能・消費電力・コストを最適化する高度なパッケージングに焦点を当てている。

アプライド マテリアルズのセミコンダクタ プロダクトグループ プレジデント、プラブー・ラジャ氏は次のように述べている。

「半導体がますます複雑化する中、当社はマテリアルズ エンジニアリングのブレークスルーを推進してAIスケーリングに必要な性能と電力効率向上を提供します。私たちはお客様とより早期から深く協力し、ロジック、メモリ、先進パッケージングの各分野で主要なデバイス変革を加速するソリューションを共同開発しています」

新ボンディング装置KinexTM:高性能・低消費電力の先端ロジック/メモリチップ製造を実現

最先端のGPUやハイパフォーマンス コンピューティング(HPC)チップでは、複数のチップレットを組み合わせ複雑なシステムを構成する先進的パッケージング手法を用いて、性能と電力効率の最適化を図っている。ハイブリッドボンディングは、近年台頭しつつあるチップ積層技術の一つで、CuとCuを直接接合できるため、性能、消費電力、コストが全般的に大きく改善される。

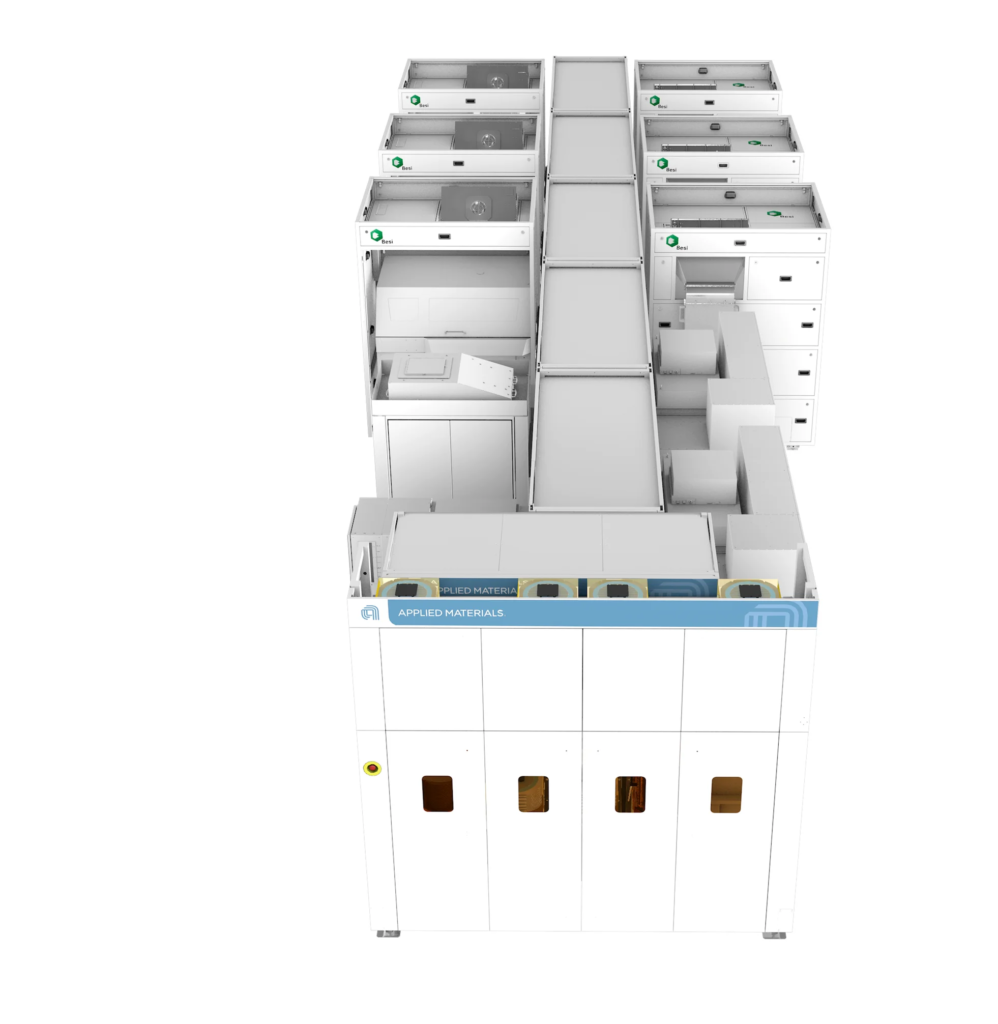

チップパッケージが複雑化するにつれ、ハイブリッドボンディングの量産には新たな課題が生じている。アプライド マテリアルズは、先端ロジックおよびメモリチップへのハイブリッドボンディング導入を促すため、BE Semiconductor Industries N.V.(Besi)と提携して業界初の統合型Die-to-Waferハイブリッドボンディング装置KinexTMを開発した。この装置には、前工程のウェーハとチップ加工におけるアプライド マテリアルズの専門知識と、先進的なダイプレースメント、配線、アセンブリのソリューションで知られるBesiの高い接合精度とスピードが融合されている。

KinexTMではハイブリッドボンディング工程の重要工程すべてが1台に統合されているため、非統合型のアプローチに比べて大きな利点が得られる。

•ダイレベルのトレーシング性能に優れ、複雑なマルチダイパッケージの管理が容易

•高精度の接合と管理されたクリーンな環境により、細密な配線ピッチを実現

•ハイブリッドボンディング工程間の待ち時間を厳密に管理することで、接合の一貫性と品質を改善

•一体型のインライン計測により、高速なオーバーレイ計測とドリフト検出

KinexTMはすでに大手ロジック/メモリメーカーならびにOSAT*各社で活用されている。

新製品CenturaTM XteraTM Epi:2nm以降のGAAトランジスタを高性能化

トランジスタチャネルを形成するソース/ドレイン構造は、最先端GAAトランジスタの性能と信頼性を左右する重要なフィーチャーの1つ。ソース/ドレインの形成には、エピタキシャル工程を用いて深いトレンチ内に材料を正確に成膜することが求められる。従来のエピタキシャル装置では、3D GAAトランジスタのソース/ドレインに求められる高アスペクト比トレンチの充填が難しく、ボイドの発生や不均一なエピ成長によって性能と信頼性が低下する。

この課題を解決してチップ性能の最大化を図るためにアプライド マテリアルズが開発したのが、CenturaTM XteraTM Epi。XteraTMは独自の低容量チャンバアーキテクチャを採用し、プリクリーン工程とエッチング工程を統合してボイドフリーのGAAソース/ドレイン構造を実現するとともに、ガスの消費量を従来のエピ装置に比べて50%削減した。革新的な「成膜&エッチングプロセス」により、トレンチ側壁や底部に材料が成膜されるにつれてトレンチの開口寸法を連続的に調節し、ウェーハ上の数十億個ものトランジスタのエピ成長をボイドフリーで最適化して、セル間の均一性を40%以上改善する。

XteraTMは大手ロジック/メモリチップメーカーに採用されている。

新登場のPROVisionTM 10 eBeam計測装置:複雑な3Dチップの歩留まりを改善

アプライド マテリアルズのイメージング&プロセス コントロール グループ バイスプレジデント、Keith Wells氏は次のように話している。

「ロジックやメモリ分野では3Dアーキテクチャの利用拡大により、光学技術の限界を超える新たなメトロロジー課題が生じています。当社はイメージング分解能とスループットの両面でeBeam技術を進化させ、チップメーカーが複雑な設計の歩留まりを加速できるよう支援しています」

新製品PROVisionTM 10は最先端ロジックチップ(GAAトランジスタやバックサイド パワーデリバリー アーキテクチャを含む)、次世代DRAMや3D NANDチップ向けに設計された最先端eBeamメトロロジーシステム。業界で初めて冷陰極電界放出(CFE: Cold Field Emission)技術を計測装置に採用し、従来の熱電界放出(TFE: Thermal Field Emission)技術に比べてナノスケールの解像度を最大50%高めたほか、描画速度は最大10倍に達す。PROVisionTM 10のサブナノメートル イメージング機能は、3Dチップの複数レイヤを透過する統合的な多層イメージを可視化する。これにより従来の光学装置の限界を超えたダイレクトオンデバイスオーバーレイ計測が可能なほか、高精度最小加工寸法(CD)計測も可能となる。EUVレイヤのオーバーレイやナノシートの計測、GAAトランジスタのエピボイド検出といった重要なプロセス制御タスクもサポートし、2nm以降のデバイスやHBMインテグレーションに不可欠な装置となっている。

PROVisionTM 10は複数の大手ロジック/メモリチップメーカーに採用されている。

*OSAT = Outsourced Semiconductor Assembly and Test(半導体後工程受託企業)

- カテゴリー

- コンバーティングプロダクツ&テクノロジー