アーカイブ情報

2025/11/27

【高弾性率ポリイミド】東レ、半導体ウェハの薄膜化に対応した新規仮貼り材料を開発

東レは、AI半導体に用いられる次世代高帯域幅メモリ(HBM※1)、SSDなどに用いられるNAND型フラッシュメモリ、xEVや産業機器に用いられるパワー半導体など、最薄で厚さ30μm以下の超薄膜半導体チップの製造に必要な半導体後工程材料(以下、「本材料」)を新たに開発し、サンプルワークを開始した。今後は、既存の量産インフラを活用して量産体制を整え、2028年までの量産化を目指す。

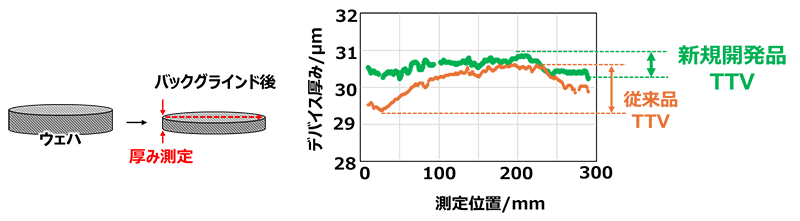

AI・高速通信の拡大に伴い、世界全体のデータ生成量は年率平均30%のペースで増加している。これらの膨大なデータを処理する半導体の性能向上が求められている中、さらなる処理能力の向上を図るには、半導体チップの積層数を増加しつつ半導体チップをより薄型化することが必要であった。また、パワー半導体では、低消費電力化や応答速度向上のため、薄型化が求められる。同材料は、弾性率を同社従来材料比で2.5倍に増加させ、バックグラインド工程※2中の半導体プロセス材料の変形を抑制し、ウェハにかかる圧力が均等化することで、薄化後のウェハのTTV※3を1.0μm未満に抑えることに成功した。

膨大なデータ処理に求められる半導体性能の向上に不可欠なトランジスタや配線の微細化は限界に近づきつつあり、従来技術の延長では対応は困難になっている。そこで新たに複数の半導体チップを垂直方向に積層する技術が、処理能力を飛躍的に向上させる手法として拡大しつつある。

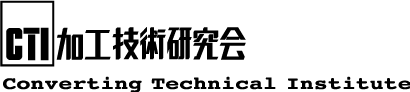

AI半導体に用いられるHBMや【図1】、NAND型フラッシュメモリも、この垂直集積技術により高い処理性能を実現しており、次世代の半導体設計において重要な役割を担っている。

一方で、一般的に半導体チップは、後工程において半導体ウェハから切りだされ個片化することで得られるが、薄型化を実現するには、個片化前のウェハに対してバックグラインド処理を行って、ウェハ自体を薄くする必要がある。

このバックグラインド工程では、ウェハをキャリア基板※4に一時的に固定し、バックグラインド後にキャリア基板から薄化したウェハを剥離するプロセスが用いられる。この際に使用される後工程材料は、仮貼り材料※5と呼ばれている。

東レは、高耐熱性樹脂であるポリイミドをベースに半導体・ディスプレイ向けの仮貼り材料を開発・量産している。今回、バックグラインド工程向けの仮貼り材料として、本材料を新たに設計・開発し、量産で使用される12インチサイズのシリコンウェハを用いて、高い均一性でウェハを極限まで薄くできることを実証した【図2】【図3】。さらに、環境負荷低減の観点から、本材料はPFASフリー※6、およびNMPフリー※7に対応している。

東レは、コア技術である「有機合成化学」、「高分子化学」、「バイオテクノロジー」、「ナノテクノロジー」を駆使し、社会を本質的に変える力のある革新的な素材の研究・技術開発を推進することで、企業理念である「わたしたちは新しい価値の創造を通じて社会に貢献します」の具現化に取り組んいく方針だ。

※1 HBM(High Bandwidth Memory):非常に高いデータ転送速度を持ったメモリであり、AI半導体において、GPUが膨大なデータをリアルタイムで処理するために、そのデータを迅速に供給する役割を果たす

※2 バックグラインド工程:半導体製造においてウェハを薄くするための工程であり、チップの小型化やパッケージの高密度化に不可欠なプロセス

※3 TTV(Total Thickness Variation):ウェハの最も厚い部分と最も薄い部分の厚みの差を表す

※4 キャリア基板:加工対象のウェハを一時的に貼り付けて支持するための基板です。特にウェハを薄化すると、ウェハが反ったり、破損したりするため、それを防ぐ役割を果たす

※5 仮貼り材料:加工対象のウェハと、キャリア基板を一時的に接着するための材料です。加工中は剥離することがなく、加工後には容易に剥離できることが求めらる

※6 PFASフリー:環境や健康への影響から規制が進んでいるPFAS(ピーファス:Per- and Polyfluoroalkyl Substances、ペルフルオロアルキルおよびポリフルオロアルキル化合物)を含まないことを意味する

※7 NMPフリー:環境や健康への影響から規制が進んでいるNMP(N-メチル-2-ピロリドン)を含まないことを意味する

- カテゴリー

- コンバーティングニュース